Latch Verilog Model . When the clock is high, d flows through to q and is transparent, but when the clock is low the latch holds its output q even if d changes. create and add the verilog module that will model the d latch using dataflow modeling. Assign 2 units delay to each assignment. latches can create problems for timing analysis tools. They also don't map to certain (fpga) architectures. A latch has two inputs : Verilog provides latch models that. Data (d), clock (clk) and one output: to represent latches in verilog, appropriate coding techniques must be applied. in this article we will look at how transparent latches are synthesized from if statements and how to avoid the inadvertent creation of latches when.

from studylib.net

When the clock is high, d flows through to q and is transparent, but when the clock is low the latch holds its output q even if d changes. Assign 2 units delay to each assignment. to represent latches in verilog, appropriate coding techniques must be applied. A latch has two inputs : They also don't map to certain (fpga) architectures. latches can create problems for timing analysis tools. Data (d), clock (clk) and one output: in this article we will look at how transparent latches are synthesized from if statements and how to avoid the inadvertent creation of latches when. Verilog provides latch models that. create and add the verilog module that will model the d latch using dataflow modeling.

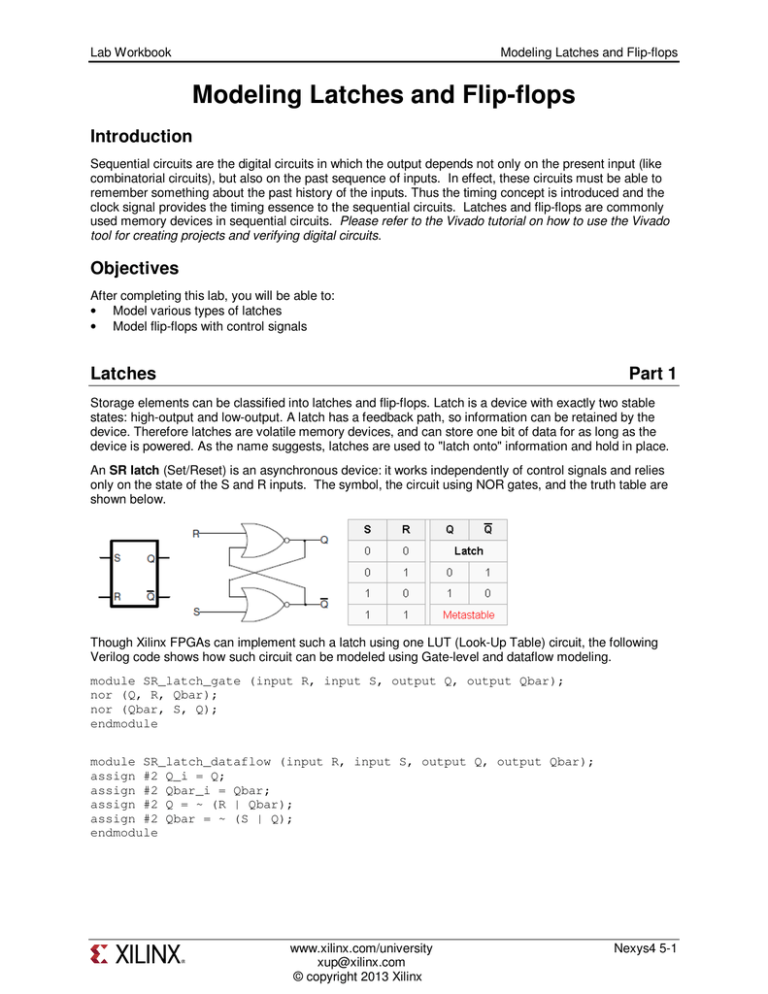

Modeling Latches and Flipflops

Latch Verilog Model Data (d), clock (clk) and one output: to represent latches in verilog, appropriate coding techniques must be applied. Data (d), clock (clk) and one output: latches can create problems for timing analysis tools. When the clock is high, d flows through to q and is transparent, but when the clock is low the latch holds its output q even if d changes. They also don't map to certain (fpga) architectures. A latch has two inputs : in this article we will look at how transparent latches are synthesized from if statements and how to avoid the inadvertent creation of latches when. create and add the verilog module that will model the d latch using dataflow modeling. Assign 2 units delay to each assignment. Verilog provides latch models that.

From www.chegg.com

Solved Latches, flipflop synchronous and asynchronous mode Latch Verilog Model When the clock is high, d flows through to q and is transparent, but when the clock is low the latch holds its output q even if d changes. A latch has two inputs : in this article we will look at how transparent latches are synthesized from if statements and how to avoid the inadvertent creation of latches. Latch Verilog Model.

From www.slideserve.com

PPT Verilog Modules for Common Digital Functions PowerPoint Latch Verilog Model Data (d), clock (clk) and one output: When the clock is high, d flows through to q and is transparent, but when the clock is low the latch holds its output q even if d changes. A latch has two inputs : They also don't map to certain (fpga) architectures. create and add the verilog module that will model. Latch Verilog Model.

From www.slideserve.com

PPT Digital System Design PowerPoint Presentation, free download ID Latch Verilog Model create and add the verilog module that will model the d latch using dataflow modeling. When the clock is high, d flows through to q and is transparent, but when the clock is low the latch holds its output q even if d changes. Data (d), clock (clk) and one output: Verilog provides latch models that. latches can. Latch Verilog Model.

From www.slideserve.com

PPT VERILOG Synthesis Combinational Logic PowerPoint Presentation Latch Verilog Model They also don't map to certain (fpga) architectures. in this article we will look at how transparent latches are synthesized from if statements and how to avoid the inadvertent creation of latches when. When the clock is high, d flows through to q and is transparent, but when the clock is low the latch holds its output q even. Latch Verilog Model.

From www.slideserve.com

PPT Digital System Design PowerPoint Presentation, free download ID Latch Verilog Model Verilog provides latch models that. to represent latches in verilog, appropriate coding techniques must be applied. When the clock is high, d flows through to q and is transparent, but when the clock is low the latch holds its output q even if d changes. create and add the verilog module that will model the d latch using. Latch Verilog Model.

From studylib.net

Modeling Latches and Flipflops Latch Verilog Model Assign 2 units delay to each assignment. create and add the verilog module that will model the d latch using dataflow modeling. latches can create problems for timing analysis tools. Data (d), clock (clk) and one output: A latch has two inputs : Verilog provides latch models that. When the clock is high, d flows through to q. Latch Verilog Model.

From www.youtube.com

verilog code for exor gate using nand gate Structural Modelling style Latch Verilog Model Verilog provides latch models that. to represent latches in verilog, appropriate coding techniques must be applied. in this article we will look at how transparent latches are synthesized from if statements and how to avoid the inadvertent creation of latches when. Data (d), clock (clk) and one output: When the clock is high, d flows through to q. Latch Verilog Model.

From www.chegg.com

Solved Sequential Logic; Active High/Low SR latch Design Latch Verilog Model to represent latches in verilog, appropriate coding techniques must be applied. Verilog provides latch models that. create and add the verilog module that will model the d latch using dataflow modeling. latches can create problems for timing analysis tools. They also don't map to certain (fpga) architectures. Assign 2 units delay to each assignment. in this. Latch Verilog Model.

From www.slideserve.com

PPT Introduction to Verilog PowerPoint Presentation, free download Latch Verilog Model in this article we will look at how transparent latches are synthesized from if statements and how to avoid the inadvertent creation of latches when. to represent latches in verilog, appropriate coding techniques must be applied. Assign 2 units delay to each assignment. create and add the verilog module that will model the d latch using dataflow. Latch Verilog Model.

From www.slideserve.com

PPT Outline PowerPoint Presentation, free download ID1883776 Latch Verilog Model Verilog provides latch models that. A latch has two inputs : latches can create problems for timing analysis tools. They also don't map to certain (fpga) architectures. in this article we will look at how transparent latches are synthesized from if statements and how to avoid the inadvertent creation of latches when. Assign 2 units delay to each. Latch Verilog Model.

From www.slideserve.com

PPT Verilog For Computer Design PowerPoint Presentation, free Latch Verilog Model create and add the verilog module that will model the d latch using dataflow modeling. They also don't map to certain (fpga) architectures. Assign 2 units delay to each assignment. A latch has two inputs : Data (d), clock (clk) and one output: in this article we will look at how transparent latches are synthesized from if statements. Latch Verilog Model.

From vlsiweb.com

Modelling Flipflops and Latches in Verilog Latch Verilog Model A latch has two inputs : to represent latches in verilog, appropriate coding techniques must be applied. in this article we will look at how transparent latches are synthesized from if statements and how to avoid the inadvertent creation of latches when. When the clock is high, d flows through to q and is transparent, but when the. Latch Verilog Model.

From www.youtube.com

Sequential Circuit Design, D Latch, D flipflop, JK flipflop, Counter Latch Verilog Model Assign 2 units delay to each assignment. When the clock is high, d flows through to q and is transparent, but when the clock is low the latch holds its output q even if d changes. latches can create problems for timing analysis tools. create and add the verilog module that will model the d latch using dataflow. Latch Verilog Model.

From www.slideserve.com

PPT ECE 4680 Computer Architecture Verilog Presentation I. PowerPoint Latch Verilog Model Verilog provides latch models that. latches can create problems for timing analysis tools. in this article we will look at how transparent latches are synthesized from if statements and how to avoid the inadvertent creation of latches when. Assign 2 units delay to each assignment. When the clock is high, d flows through to q and is transparent,. Latch Verilog Model.

From www.youtube.com

Verilog Tutorial 20 Latch YouTube Latch Verilog Model latches can create problems for timing analysis tools. Verilog provides latch models that. create and add the verilog module that will model the d latch using dataflow modeling. Data (d), clock (clk) and one output: to represent latches in verilog, appropriate coding techniques must be applied. When the clock is high, d flows through to q and. Latch Verilog Model.

From www.youtube.com

數位邏輯實驗Lab9 2 Verilog Model for D Latch and D Flip Flop YouTube Latch Verilog Model When the clock is high, d flows through to q and is transparent, but when the clock is low the latch holds its output q even if d changes. They also don't map to certain (fpga) architectures. latches can create problems for timing analysis tools. Data (d), clock (clk) and one output: Assign 2 units delay to each assignment.. Latch Verilog Model.

From www.youtube.com

verilog code for SR FLIP FLOP with testbench YouTube Latch Verilog Model in this article we will look at how transparent latches are synthesized from if statements and how to avoid the inadvertent creation of latches when. Data (d), clock (clk) and one output: to represent latches in verilog, appropriate coding techniques must be applied. Verilog provides latch models that. They also don't map to certain (fpga) architectures. When the. Latch Verilog Model.

From mungfali.com

Verilog Structural Model Latch Verilog Model A latch has two inputs : create and add the verilog module that will model the d latch using dataflow modeling. Verilog provides latch models that. When the clock is high, d flows through to q and is transparent, but when the clock is low the latch holds its output q even if d changes. to represent latches. Latch Verilog Model.